# **MACHAKOS UNIVERSITY**

## University Examinations for 2021/2022 Academic Year

# SCHOOL OF ENGINEERING AND TECHNOLOGY

# DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING

# THIRD YEAR SECOND SEMESTER EXAMINATIONS FOR

# **BACHELOR OF SCIENCE (MECHANICAL ENGINEERING)**

# **EMM 300: ENGINEERING ELECTRONICS**

#### DATE:

TIME: 2 Hours

### **INSTRUCTIONS**

Answer Question One And Any Other Two Questions

## QUESTION ONE (COMPULSORY) (30 MARKS)

- a) A diode whose internal resistance is  $20\Omega$  is to supply power to a 1000  $\Omega$  load from a 110 V (rms) source of supply. Calculate:

- i. The peak load current;

- ii. The DC load current;

- iii. AC Load Current;

- iv. The DC diode voltage;

(8 marks)

- b) Determine the dc bias voltage  $V_{CE}$  and the current  $I_C$  for the CE BJT voltage divider circuit configuration. Assume  $V_{CC} = 22 \text{ V}$ ,  $R_1 = 39 \text{ k}\Omega$ ,  $R_2 = 3.9 \text{ k}\Omega$ ,  $R_C = 10 \text{ k}\Omega$ ,  $R_E = 1.5 \text{ k}\Omega$  and  $\beta = 100$ . (8 marks)

- c) Simplify the following Boolean expressions using Boolean algebra and/or De Morgan's theorem.

- i.

$$\overline{\left(A+\overline{B}\right)\left(\overline{A\overline{C}\overline{D}}\right)}$$

ii.

$$\left(\overline{\overline{A}\oplus\overline{BC}}\right)\left(\overline{A+B+\overline{C}}\right)$$

(6 marks)

d) Assuming that all numbers are 8 bits wide, complete the missing entries, which are not shaded, in the following table. (No marks will be awarded for this question unless you show how the solution is derived.)

| Hexadecimal | Octal | Signed<br>binary | Signed<br>decimal |

|-------------|-------|------------------|-------------------|

| ?           |       | ?                | -105              |

| ?           | 275   |                  | ?                 |

#### **QUESTION TWO (20 MARKS)**

- a) Describe the following regions of operation of a common emitter transistor amplifier:

- (i) Cut-off;

- (ii) Active;

- (iii) Saturation.

(6 marks)

(8 marks)

- b) Explain the term thermal run-away with respect to BJT circuits.

- (2 marks)

- c) A silicon transistor using the voltage divider bias method has the following parameters:  $R_1 = 33 \text{ K}\Omega$ ,  $R_2 = 15 \text{ K}\Omega$ ,  $R_C = 1\text{K}\Omega$ ,  $R_E = 680 \Omega$  and  $V_{CC} = 9 \text{ V}$ . Determine the operating point of this transistor circuit.

(5 marks)

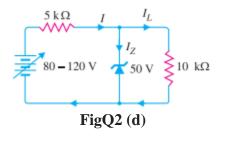

d) For the circuit shown in FigQ2 (d), find the maximum and minimum values of zener diode current.

(4 marks)

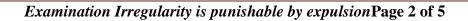

- e) i. Sketch  $v_o$  versus time for the circuit in FigQ2 (e). The input is a sine wave given by  $v_i = 10 \sin \omega t V$ . Assume  $V_{\gamma} = 0$ .

- ii. Determine the rms value of the output voltage.

#### **QUESTION THREE (20 MARKS)**

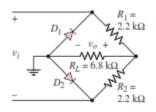

- a) i. Determine the *Q*-point values for the circuit in FigQ3 (a). Assume  $\beta = 50$

- ii. Repeat part (i) if all resistor values are reduced by a factor of 3.

(10 marks)

(3 marks)

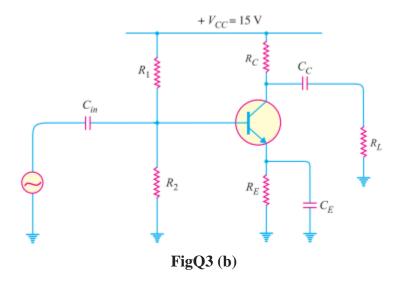

- b) For the transistor amplifier shown in FigQ3 (b)  $R_1 = 10 \text{ k}\Omega$ ,  $R_2 = 5 \text{ k}\Omega$ ,  $R_C = R_L = 1 \text{ k}\Omega$ , and  $R_E = 2 \text{ k}\Omega$

- i. Draw d.c. load line;

- ii. Determine the operating point;

- iii. Draw a.c. load line.

Assume  $V_{BE} = 0.7 V$ .

(10 marks)

#### **QUESTION FOUR (20 MARKS)**

a) Simplify the following Boolean expressions using Boolean algebra and/or De Morgan's theorem.

i.

$$\overline{ABC} + \overline{BC} + AB\overline{C}$$

ii

$\overline{(\overline{A} \oplus B)}(\overline{A} + B + BC)$

(8 marks)

b) Simplify the following Boolean equation, in product-of-sums form, using a Karnaugh map.

$f = A\overline{B} + \overline{A}BC + AB\overline{C}$

(4 marks)

c) Assuming that all numbers are 8 bits wide, complete the missing entries, which are not shaded, in the following table. (No marks will be awarded for this question unless you show how the solution is derived.)

| Hexadecimal | Octal | Unsigned | Signed  | BCD |

|-------------|-------|----------|---------|-----|

|             |       | decimal  | decimal |     |

| C5          |       | ?        | ?       |     |

| ?           | 25    |          |         | ?   |

|             |       |          |         | (0  |

(8 marks)

#### **QUESTION FIVE (20 MARKS)**

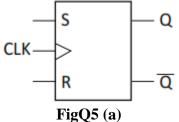

a) FigQ5 (a) shows a clocked SR-type flip-flop. Implement this flip-flop using a D-type flip-flop. You may assume that any disallowed input combinations do not occur.

(8 marks)

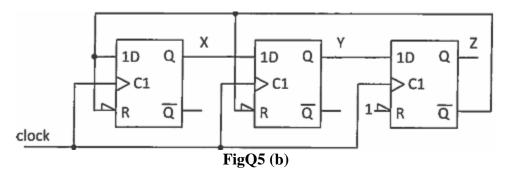

b) For the circuit shown in FigQ5 (b), complete the timing waveforms for signals X, Y, and Z for 6 clock cycles. You may assume that initially, the values of X, Y and Z are zero.

(6 marks)

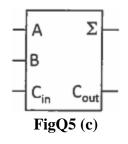

- c) A full-adder is shown in FigQ5 (c). For inputs A, B, and  $C_{in}$ , and outputs  $\sum$  and  $C_{out}$ :

- i. Draw the truth table for the circuit;

- ii. Hence, derive Boolean expression for  $\sum$  and  $C_{\text{out}}.$

(6 marks)